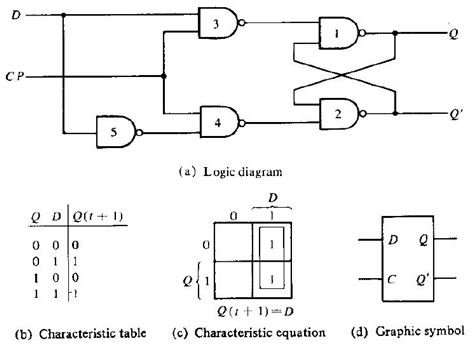

D Latch Circuit Characteristic Table

The following table shows the state table of d latch.

D latch circuit characteristic table. That means the output of d latch is sensitive to the changes in the input d as long as the enable is high. Latch is an electronic logic circuit with two stable states i e. Thus the output has two stable states based on the inputs which have been discussed below. There are many applications where separate s and r inputs not required.

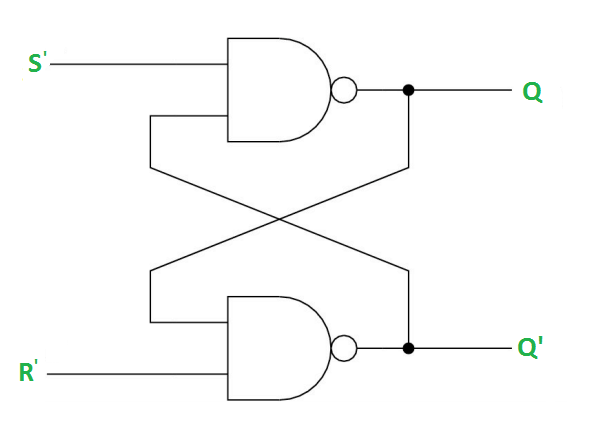

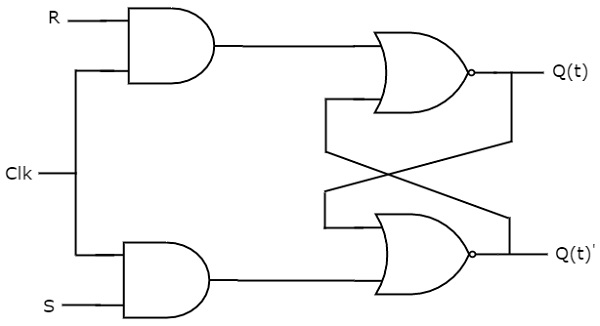

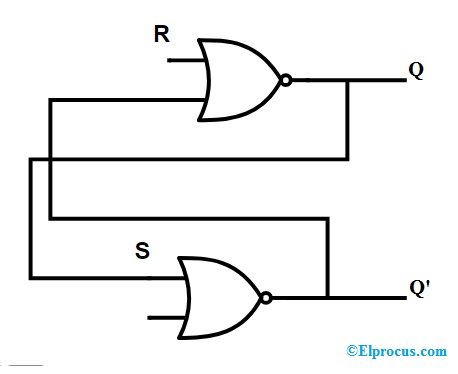

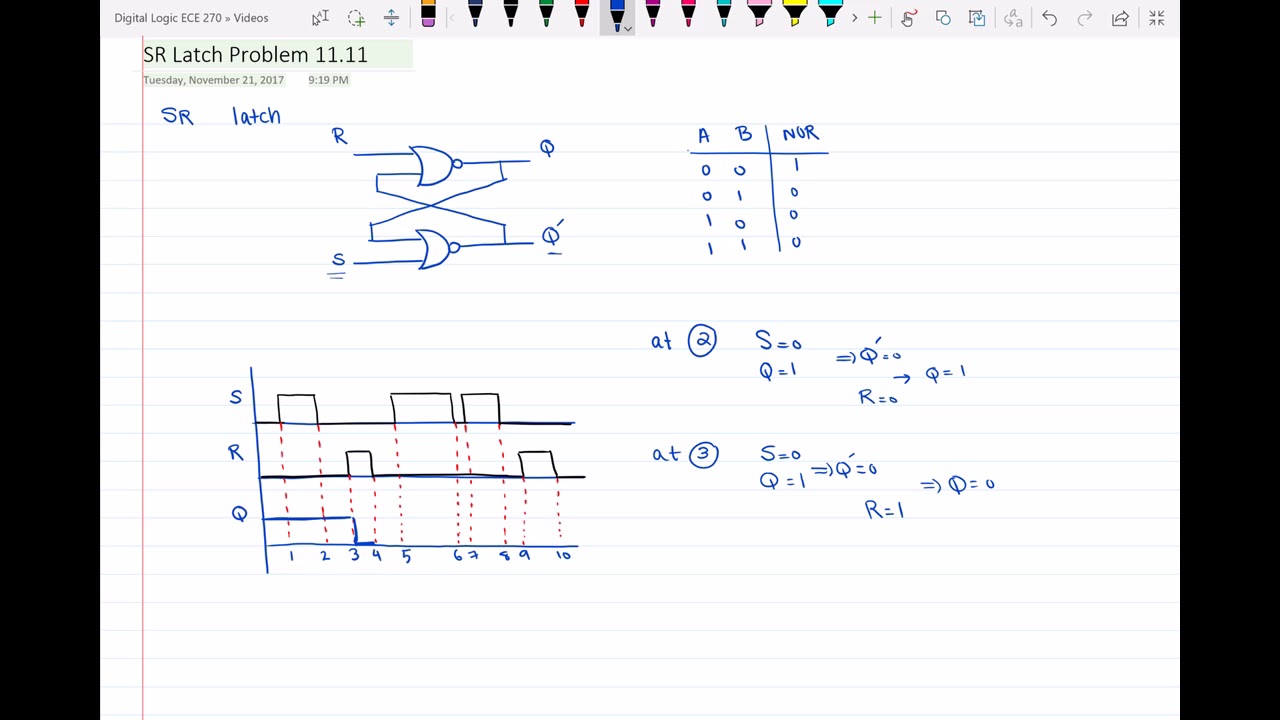

Hence a latch can be a memory device. Sr latches a sequential circuit that has two inputs set that sets the latch and reset that clears the latch and two complementary outputs. In this chapter we implemented various latches by providing the cross coupling between nor gates. Latch can store one bit of information as long as the device is powered on.

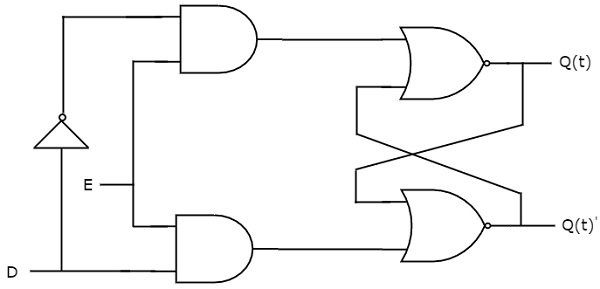

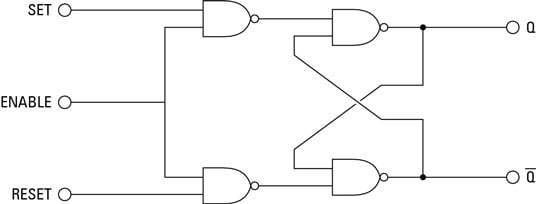

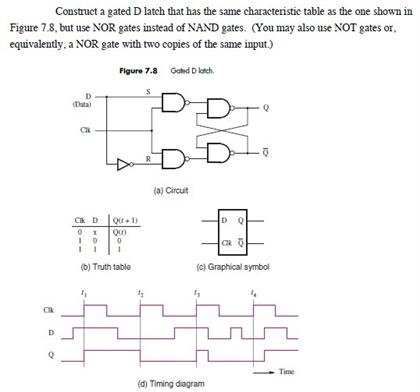

S r nor latch s r nand latch 4 1. D latch can be gated and then the logic circuit can be as follows gated d latch. For this reason d latch is sometimes called a transparent latch. In this situation the latch is said to be open and the path from the input d to the output q is transparent.

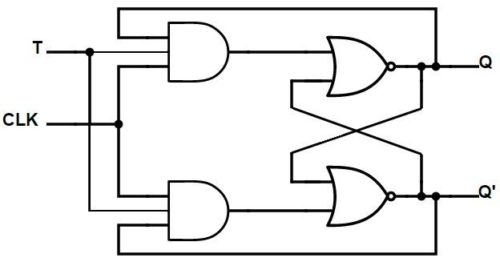

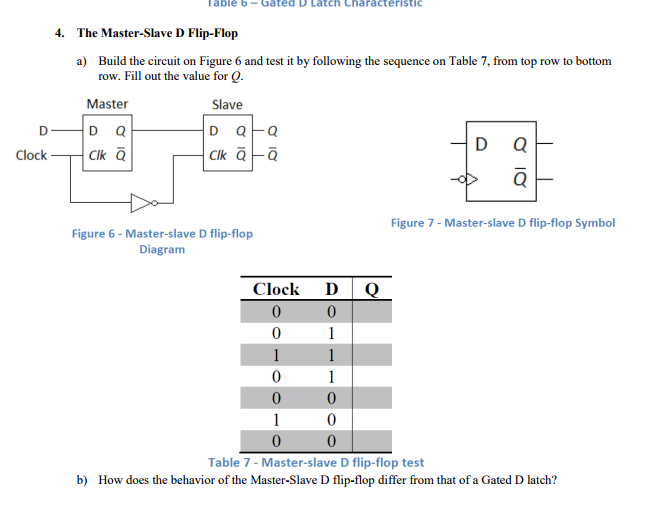

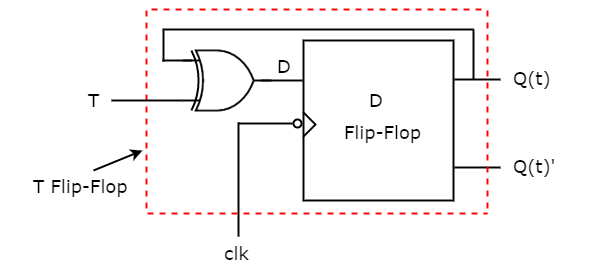

Thus d flip flop is a controlled bi stable latch where the clock signal is the control signal. When e is 0 the latch is disabled or closed and the q output retains its last value independent of the d input. In these cases by creating d flip flop we can omit the conditions where s r 0 and s r 1. Q n 1 en d en q n.

When enable is asserted latch immediately. Thus the circuit is also known as a transparent latch. Looking at the truth table for d latch with enable input and simplifying q n 1 function by k map we get the characteristic equation for d latch with enable input as. Unlike the combinational circuits the outputs of the latch are not uniquely determined by the current inputs.

It is a bistable multivibrator. Characteristic tables s r q n 1 0 0 q n 0 1 00 1 0 11. Again this gets divided into positive edge triggered d flip flop and negative edge triggered d flip flop. As shown in the truth table the q output follows the d input.

Latch has a feedback path to retain the information. Truth table characteristic table and excitation table for d flip flop contribute. So when the device is disabled e 0 it holds its current value and when enabled e 1 it can be set or reset i e. Truth tables characteristic equations and excitation tables of different flipflops nand and nor gate using cmos technology circuit design of a 4 bit binary counter using d flip flops.

A circuit implementation of the gated d latch is shown in figure 60.